Download Intel Xeon D-1540

Transcript

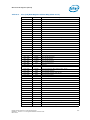

SATA Controller Registers (D31:F2) Bits 15:8 7 6:4 Description Reserved 64 Bit Address Capable (C64) — RO. Capable of generating a 32-bit message only. Multiple Message Enable (MME) — RO. = 000 (and MSIE is set), a single MSI message will be generated for all SATA ports, and bits [15:0] of the message vector will be driven from MD[15:0]. For 6 port components: MME Value Driven on MSI Memory Write Bits[15:3] Bit[2] Bit[1] Bit[0] 000, 001, 010 MD[15:3] MD[2] MD[1] MD[0] 011 MD[15:3] For 4 port components: MME Port Port Port Port Port Port 0: 1: 2: 3: 4: 5: 0 0 0 0 1 1 Port Port Port Port Port Port 0: 1: 2: 3: 4: 5: 0 0 1 1 0 0 Port Port Port Port Port Port 0: 1: 2: 3: 4: 5: 0 1 0 1 0 1 Value Driven on MSI Memory Write Bits[15:3] Bit[2] Bit[1] Bit[0] 000, 001, 010 MD[15:3] MD[2] MD[1] MD[0] 011 MD[15:3] Port Port Port Port 0: 1: 4: 5: 0 0 1 1 Port Port Port Port 0: 1: 2: 3: 0 0 0 0 Port Port Port Port 0: 1: 2: 3: 0 1 0 1 All other MME values are reserved. If this field is set to one of these reserved values, the results are undefined. Note: The CCC interrupt is generated on unimplemented port (AHCI PI register bit equal to 0). If CCC interrupt is disabled, no MSI shall be generated for the port dedicated to the CCC interrupt. When CCC interrupt occurs, MD[2:0] is dependant on CCC_CTL.INT (in addition to MME). 3:1 0 Multiple Message Capable (MMC) — RO. MMC is not supported. MSI Enable (MSIE) — R/W /RO. If set, MSI is enabled and traditional interrupt pins are not used to generate interrupts. This bit is R/W when SC.SCC is not 01h and is read-only 0 when SCC is 01h. The CMD.ID bit has no effect on MSI. Note: 8.1.32 Software must clear this bit to 0 to disable MSI first before changing the number of messages allocated in the MMC field. Software must also make sure this bit is cleared to ‘0’ when operating in legacy mode (when GHC.AE = 0). MSIMA— Message Signaled Interrupt Message Address Register (SATA–D31:F2) Address Offset: Default Value: Note: 84h–87h 00000000h Attribute: Size: R/W 32 bits There is no support for MSI when the software is operating in legacy (IDE) mode when AHCI is not enabled. Prior to switching from AHCI to IDE mode, software must make sure that MSI is disabled. Bits 31:2 1:0 Description Address (ADDR) — R/W. Lower 32 bits of the system specified message address, always DWord aligned. Reserved Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 1 of 4: Integrated Platform Controller Hub March 2015 335

Related documents

CT-CCVAX Intel Atom D2000/N2000 COM

Intel Atom E620

User Guide

Development Kits User Guide: 4th Generation Intel® Core

Intel Xeon Wolfdale E3210

Evido EAD-D2000 User`s manual

Intel Pentium G6951

Carrier Access CMG Router User manual

Black Box Compact T1 MT850A User manual

Microsoft SP5100/S Specifications