Download Intel Xeon D-1540

Transcript

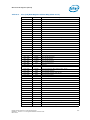

Thermal Sensor Registers (D31:F6) Bit Description 29 TT Enable (TTEN) – R/W. When set the thermal throttling states are enabled. At reset, BIOS must set bits 28:0 and then do a separate write to set bit 29 to enable throttling. SW may set bit 31 at the same time it sets bit 29 if it wishes to lock the register. If SW wishes to change the values of 28:0, it must first clear the TTEN bit, then change the values in 28:0; and then re-enable TTEN. It is legal to set bits 31, 30 and 29 with the same write. This bit must not be set by SW until SW has already enabled the thermal sensor(TSEL.ETS =’1’). If TTEN is written to ‘0’, after having been enabled, then Intel® Xeon® Processor D-1500 Product Family may stay in the throttling state it was in at the moment TTEN is disabled. There is no intent that the sensor be enabled for a while and then disabled and left off. It may be disabled temporarily while changing the register values, but it should not be left in the disabled state. 28:20 T2 Level (T2L) – R/W. When TTEN = 1 AND TSE = ‘1’ AND (T2L >= TSR[8:0] > T1L), then the system is in T2 state. When TTEN = 1 AND TSE = ‘1’ AND (TSR[8:0] > T2L), then the system is in T3 state. Note: The T3 condition overrides PMSync[13] and forces the system to T3 if both cases are true. SW NOTE:T2L must be programmed to a value greater than T1L if TTEN=’1’ 19 18:10 Reserved T1 Level (T1L) – R/W. When TTEN = 1 AND TSE = 1 AND (T1L >= TSR[8:0] > T0L), then the system is in T1 state. SW NOTE:T1L must be programmed to a value greater than T0L if TTEN=’1’ 9 8:0 16.2.11 Reserved T0 Level (T0L) – R/W. When TEMP.TSR[8:0] <= T0L OR TT.Enable is ‘0’ OR TSE 0’, then the system is in T0 state. PHL—Intel® Xeon® Processor D-1500 Product Family Hot Level Register Offset Address: Default Value: TBARB+60h 0000h Bit 15 14:9 8:0 16.2.12 RO, R/W 16 bit Description PHL Enable (PHLE) – R/W. When set and the current temperature reading, TSR, is greater than PHLL, then the TEMP_ALERT# pin will be asserted (active low). Reserved PHL Level (PHLL) – R/W. Temperature value used for TEMP_ALERT# pin. PHLC—PHL Control Register Offset Address: Default Value: TBARB+62h 00h Bit 7:1 0 16.2.13 Attribute: Size: Attribute: Size: RO, R/W 8 bit Description Reserved PHL Lock – R/W. When written to a ‘1’, then both PHL and PHLC are locked TAS — Thermal Alert Status Register Offset Address: Default Value: TBARB+80h 00h Bit 7:2 Attribute: Size: RO, R/W 8 bit Description Reserved Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 1 of 4: Integrated Platform Controller Hub March 2015 555

Related documents

CT-CCVAX Intel Atom D2000/N2000 COM

Intel Atom E620

User Guide

Development Kits User Guide: 4th Generation Intel® Core

Intel Xeon Wolfdale E3210

Evido EAD-D2000 User`s manual

Intel Pentium G6951

Carrier Access CMG Router User manual

Black Box Compact T1 MT850A User manual

Microsoft SP5100/S Specifications