Download Intel Xeon D-1540

Transcript

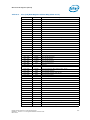

Gigabit LAN Configuration Registers Table 6-1. Gigabit LAN Configuration Registers Address Map (Gigabit LAN—D25:F0) (Sheet 2 of 2) Offset 6.1.1 Mnemonic MCTL 0080h R/W, RO MADDL Message Address Low See register description R/W D8h–dBh MADDH Message Address High See register description R/W DCh–DDh MDAT Message Data See register description R/W E0h–E1h FLRCAP Function Level Reset Capability E2h–E3h FLRCLV Function Level Reset Capability Length and Value E4h–E5h DEVCTRL Device Control 0009h RO See register description R/WO, RO 0000h R/W, RO VID—Vendor Identification Register (Gigabit LAN— D25:F0) 00h–01h 8086h Attribute: Size: RO 16 bits Bit Description 15:0 Vendor ID — RO. This is a 16-bit value assigned to Intel. The field may be auto-loaded from the NVM at address 0Dh during init time depending on the “Load Vendor/Device ID” bit field in NVM word 0Ah with a default value of 8086h. DID—Device Identification Register (Gigabit LAN—D25:F0) 02h–03h See bit description Attribute: Size: RO 16 bits Bit Description 15:0 Device ID — RO. This is a 16-bit value assigned to Intel® Xeon® Processor D-1500 Product Family Gigabit LAN controller. The field may be auto-loaded from the NVM word 0Dh during initialization time depending on the "Load Vendor/Device ID" bit field in NVM word 0Ah. PCICMD—PCI Command Register (Gigabit LAN—D25:F0) Address Offset: Default Value: Bit 15:11 10 226 Attribute D4h–D7h Address Offset: Default Value: 6.1.3 Message Control Default D2h–D3h Address Offset: Default Value: 6.1.2 Register Name 04h–05h 0000h Attribute: Size: R/W, RO 16 bits Description Reserved Interrupt Disable — R/W. This disables pin-based INTx# interrupts on enabled Hot-Plug and power management events. This bit has no effect on MSI operation. 0 = Internal INTx# messages are generated if there is an interrupt for Hot-Plug or power management and MSI is not enabled. 1 = Internal INTx# messages will not be generated. This bit does not affect interrupt forwarding from devices connected to the root port. Assert_INTx and Deassert_INTx messages will still be forwarded to the internal interrupt controllers if this bit is set. 9 Fast Back to Back Enable (FBE) — RO. Hardwired to 0. 8 SERR# Enable (SEE) — R/W. 0 = Disable 1 = Enables the Gb LAN controller to generate an SERR# message when PSTS.SSE is set. Intel® Xeon® Processor D-1500 Product Family Datasheet - Volume 1 of 4: Integrated Platform Controller Hub March 2015

Related documents

CT-CCVAX Intel Atom D2000/N2000 COM

Intel Atom E620

User Guide

Development Kits User Guide: 4th Generation Intel® Core

Intel Xeon Wolfdale E3210

Evido EAD-D2000 User`s manual

Intel Pentium G6951

Carrier Access CMG Router User manual

Black Box Compact T1 MT850A User manual

Microsoft SP5100/S Specifications